## 1、特性

- 工作频率 4.8GHz

- 积分随机抖动 35 fs rms

- 片上输入终端

- 3.3 V 电源

## 3、应用

- 低抖动时钟分配

- 时钟和数据信号恢复

- 电平转换

- 无线通信

## 2、概述

XHT-946是一款超快时钟扇出缓冲器，是一款超快时钟扇缓冲器，采用硅锗采用硅锗 (SiGe) 双极工艺制造。该器件专为要求低抖动的高速应用而设计。

器件的差分输入端配备了中心抽头、差分、100 片上终端电阻器。输入端接受直流耦合LVPECL、CML、3.3V CMOS (单端) 以及交流耦合 1.8V CMOS、LVDS 和LVPECL 输入

VREF 引脚用于为交流耦合输入提供偏置。

XHT-946具有六个全摆幅发射极耦合逻辑(ECL) 输出驱动器。

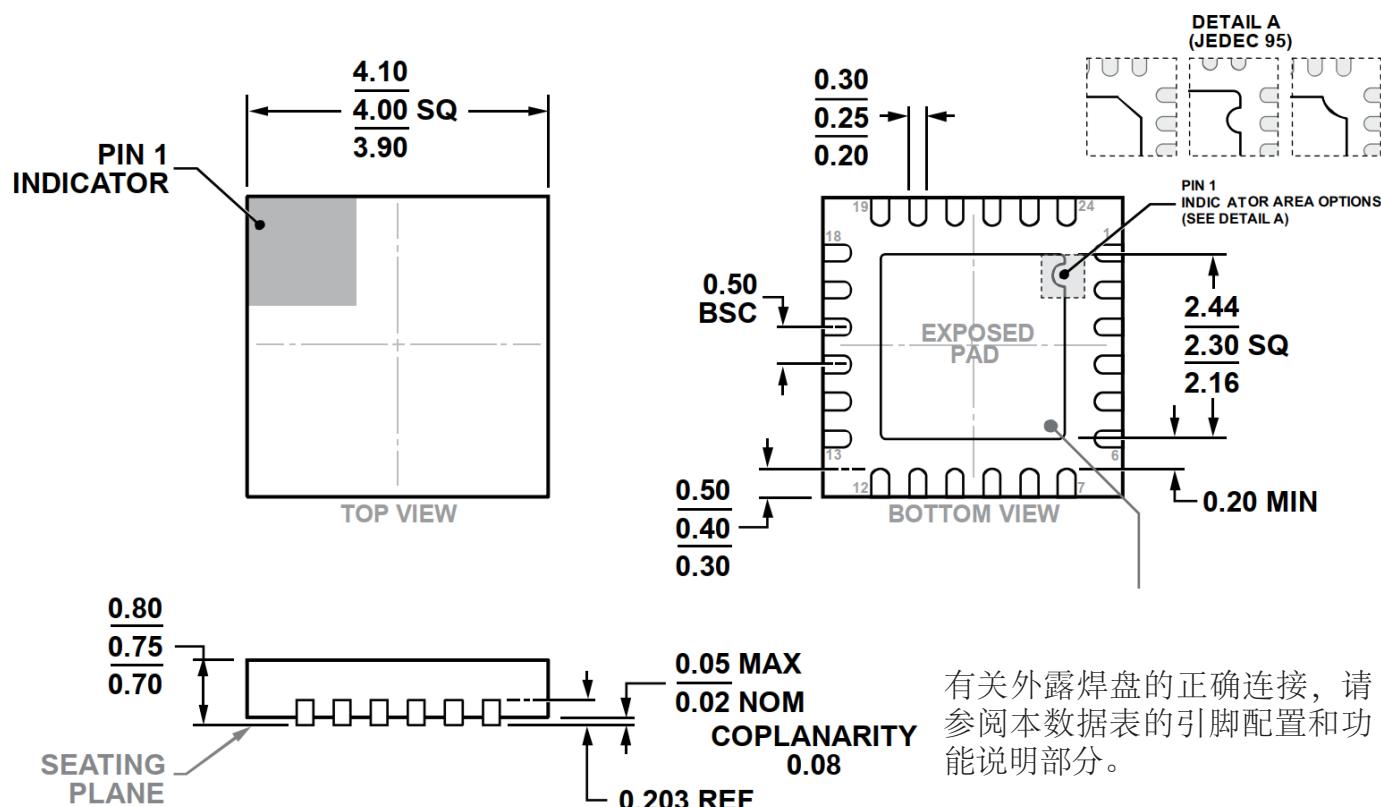

XHT-946 采用采用 24 引线 QFN封装，可在 -55° C 至 +125° C 的温度范围内工作。

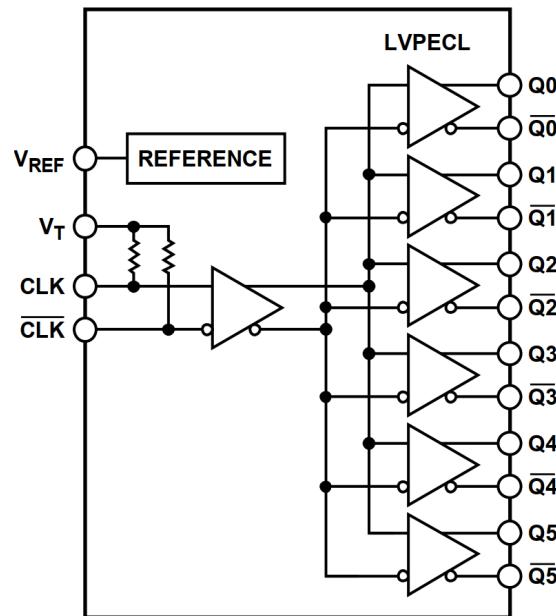

## 4、功能框图

图 1. 功能框图

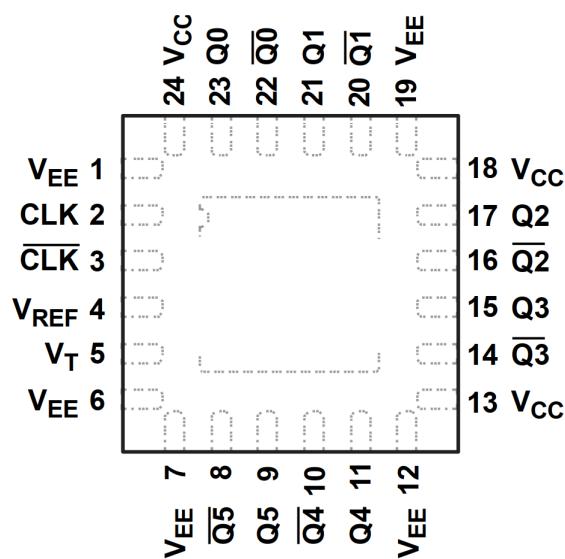

## 5、引脚描述

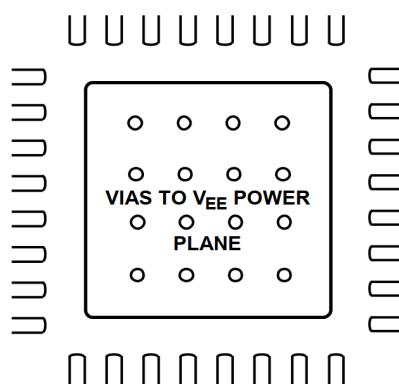

图 2. 芯片封装引脚分布

| 名称               | 编号          | 功能                                         |

|------------------|-------------|--------------------------------------------|

| V <sub>EE</sub>  | 1,6,7,12,19 | 负电源引脚                                      |

| CLK              | 2           | 差分输入同相端                                    |

| CLK̄             | 3           | 差分输入反相端                                    |

| V <sub>REF</sub> | 4           | 基准电压。该引脚为交流耦合 CLK 和 CLK̄ 输入提供偏置参考电压。       |

| V <sub>T</sub>   | 5           | 中心抽头。该引脚为 CLK 和 CLK̄ 输入提供 100 Ω 输入电阻的中心抽头。 |

| Q5, Q5̄          | 8、9         | 差分 LVPECL 输出                               |

| Q4, Q4̄          | 10、11       | 差分 LVPECL 输出                               |

| V <sub>CC</sub>  | 13、18、24    | 正电源引脚                                      |

| Q3, Q3̄          | 14、15       | 差分 LVPECL 输出                               |

| Q2, Q2̄          | 16、17       | 差分 LVPECL 输出                               |

| Q1, Q1̄          | 20、21       | 差分 LVPECL 输出                               |

| Q0, Q0̄          | 22、23       | 差分 LVPECL 输出                               |

| EPAD             |             | EPAD 必须焊接到 VEE 上                           |

## 7、电气特性

若无特别说明，V<sub>CC</sub> - V<sub>EE</sub> = 3.3 V 和 -55°C ≤ T<sub>A</sub> ≤ +125°C。

| 参数            | 符号               | 测试条件                                  | 最小值  | 典型值 | 最大值  | 单位               |

|---------------|------------------|---------------------------------------|------|-----|------|------------------|

| <b>直流输入特性</b> |                  |                                       |      |     |      |                  |

| 高电平输入电压       | V <sub>IH</sub>  |                                       | 1.6  | -   | 3.3  | V                |

| 低电平输入电压       | V <sub>IL</sub>  |                                       | 0    | -   | 3    | V                |

| 输入差分范围        | V <sub>ID</sub>  | 输入引脚之间为 ±1.7 V                        | 0.4  | -   | 3.3  | V <sub>p-p</sub> |

| 差分输入共模电平      | V <sub>ICM</sub> |                                       | 1.5  | -   | 3.2  | V                |

| 输入漏电流         | I <sub>IN</sub>  |                                       | -    | -   | 40   | μA               |

| 电源电流          | I <sub>CC</sub>  |                                       | -    | -   | 320  | mA               |

| <b>直流输出特性</b> |                  |                                       |      |     |      |                  |

| 高电平输出电压       | V <sub>OH</sub>  | 输出负载 50 Ω to 1.3V                     | 2.04 | -   | 2.54 | V                |

| 低电平输出电压       | V <sub>OL</sub>  | 输出负载 50 Ω to 1.3 V                    | 1.31 | -   | 1.76 | V                |

| 输出幅度          | V <sub>O</sub>   | 单端到地 V <sub>OH</sub> -V <sub>OL</sub> | 0.61 | -   | 0.96 | V                |

| 参考电压          | V <sub>REF</sub> |                                       |      |     |      |                  |

| 参考输出电压        |                  | -500 μA to +500 μA                    | 2    | -   | 2.3  | V                |

| 参考输出电阻        |                  | 设计保证                                  | 220  | -   | 250  | Ω                |

| 参数                                                                         | 符号        | 测试条件                                                                                    | 最小值 | 典型值  | 最大值  | 单位     |

|----------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------|-----|------|------|--------|

| <b>动态交流电性能</b>                                                             |           |                                                                                         |     |      |      |        |

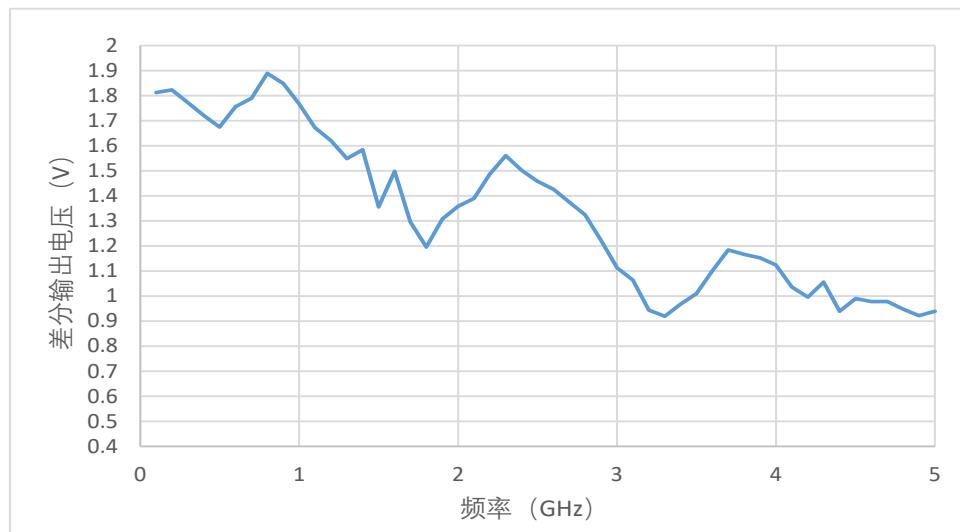

| 最大工作频率                                                                     | $f_{max}$ | 差分输出电压如图 4 所示, >0.8 V<br>差分输出摆幅                                                         | 4.8 | -    | -    | GHz    |

| 输出上升 / 下降时间                                                                |           | 20% 至 80% 以不同方式测量                                                                       | -   | -    | 90   | ps     |

| 传输延时                                                                       |           | $V_{ICM} = 2 \text{ V}, V_{ID} = 1.6 \text{ V p-p}$                                     | -   | 200  | 220  | ps     |

| 输出端偏移                                                                      |           |                                                                                         | -   | 25   | 50   | ps     |

| 积分随机抖动                                                                     |           | $BW = 12 \text{ kHz} - 20 \text{ MHz}, CLK = 1 \text{ GHz}$<br>$T_A = 25^\circ\text{C}$ | -   | 35   | 62   | fs rms |

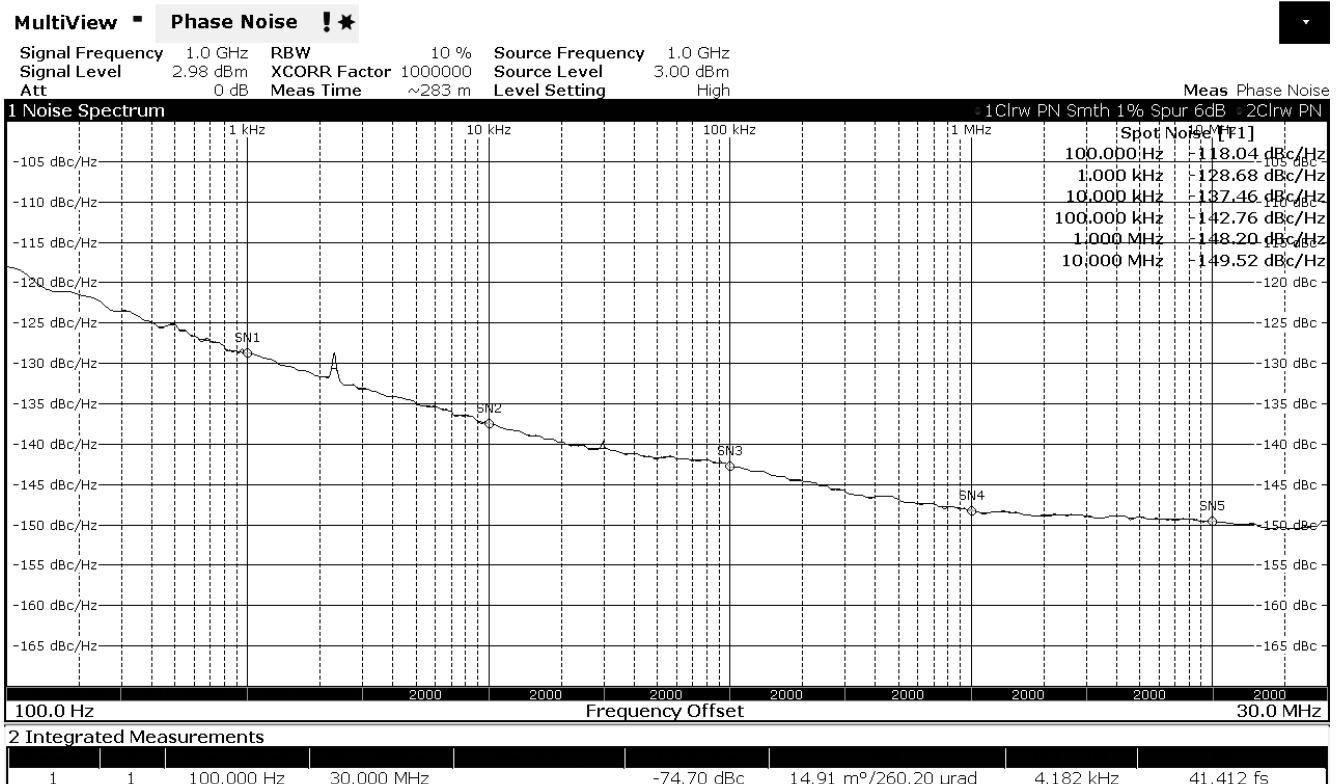

| <b>动态时钟输出相位噪声 (输入压摆率 &gt; 1 V/ns, <math>T_A = 25^\circ\text{C}</math>)</b> |           |                                                                                         |     |      |      |        |

| $f_{IN}=1\text{GHz}$                                                       | PN        | SR@ 100 Hz 偏移                                                                           |     | -115 | -110 | dBc/Hz |

|                                                                            |           | SR@ 1 kHz 偏移                                                                            |     | -127 | -122 | dBc/Hz |

|                                                                            |           | SR@ 10 kHz 偏移                                                                           |     | -142 | -137 | dBc/Hz |

|                                                                            |           | SR@ 100 kHz 偏移                                                                          |     | -147 | -142 | dBc/Hz |

|                                                                            |           | SR@ 1 MHz 偏移                                                                            |     | -153 | -143 | dBc/Hz |

|                                                                            |           |                                                                                         |     |      |      |        |

## 8、特性曲线

图 3. frequency offset vs 相噪

图 4. 差分输出电压 vs 频率

## 9、功能描述

### 9.1 时钟输入

XHT-946 接受差分时钟输入，并将其分配到所有六个 LVPECL 输出。输出电压摆幅达到标准LVPECL 摆幅 50% 时的频率是最大标称频率。该器件有一个差分输入端，配有中心抽头、差分、100 片上终端电阻。输入可接受直流耦合LVPECL、CML、3.3 V CMOS（单端）和交流耦合 1.8 V CMOS、LVDS 和LVPECL 输入。VREF 引脚可用于交流耦合输入的偏置。

将差分输入电压摆幅保持在约 400 mVp-p 和 3.4 Vp-p 之间。输入压摆率低于 1 V/ns 会降低输出抖动性能。在宽输入压摆率范围内，XHT-946 可以大幅减少随机抖动。建议尽量使用快速肖特基二极管钳位过大的输入信号，因为衰减器会降低压摆率。输入信号长度超过几厘米时，应使用低损耗电介质或具有良好高频特性的电缆。

### 9.2 时钟输出

要达到规定的性能，必须使用适当的传输线终端。XHT-946 的 LVPECL 输出可直接将 800 mV 电压驱动到 50 电缆或端接 50 以 VCC - 2V 为基准的微带/带状线内传输线上。LVPECL 输出级如图5所示。输出设计用于实现最佳传输线匹配。如果高速信号的传输距离必须超过 1 厘米，则需要采用微带或带状线技术，以确保适当的转换时间，并防止过度的输出振铃和与脉宽相关的传播延迟扩散。

图 5. LVPECL 输出级简化示意图

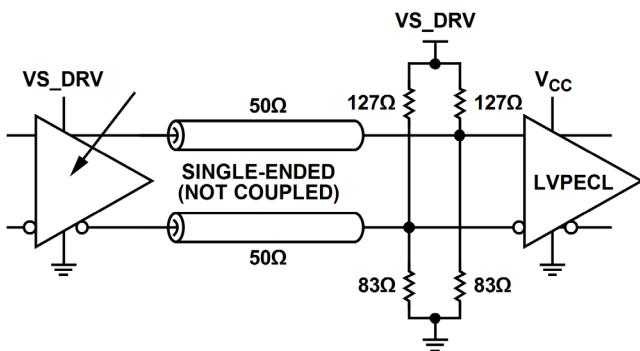

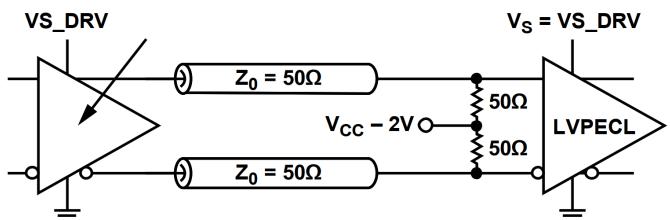

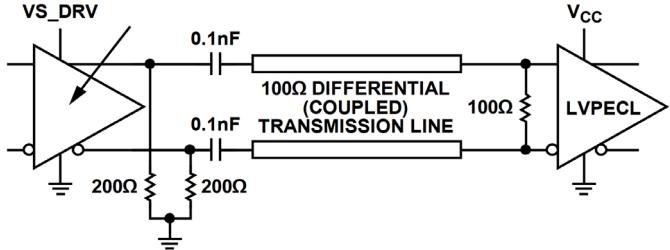

图6/7/8/9 内描述了各种LVPECL 输出端接方案。直流耦合时，接收缓冲器的VCC 应与 VS\_DRV匹配。文氏等效端使用电阻网络提供50 Ω 端接至低于LVPECL 驱动器VOL 的直流电压。在这种情况下，XHT-946 上的VS\_DRV 应等于接收缓冲器的VCC。虽然图7 中所示的电阻器组合会导致VS\_DRV - 2 V 产生直流偏置点，但实际共模电压为VS\_DRV - 1.3 V，这是因为XHT-946的LVPECL 驱动器通过下拉电阻器有额外的电流流过。

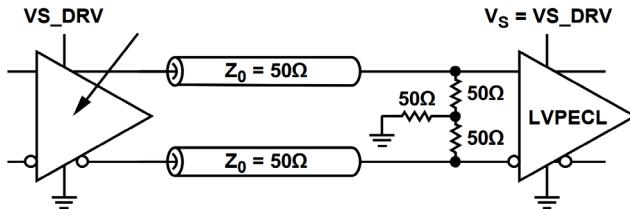

LVPECL Y 端接是一种简洁的端接方案，使用的元件最少，并能提供奇模和偶模阻抗匹配。偶模阻抗匹配是高频紧密耦合传输线的一个重要考虑因素。它的主要缺点是在改变发射极跟随器LVPECL 驱动器的驱动强度方面灵活性有限。在驱动较长的线路时，这可能是一个重要的考虑因素，但通常不是问题。

图 6. 直流耦合、3.3 V LVPECL 远端戴维南终端

图 7. 直流耦合，3.3 V LVPECL

图 8. 直流耦合、3.3 V LVPECL Y 型端接

图 9. 交流耦合、LVPECL 与平行传输线

### 9.3 PCB注意事项

XHT-946缓冲器专为超高速应用而设计。因此，必须采用高速设计技术才能实现指定的性能。作为多层电路板的一部分，负电源(VEE)和正电源(VCC)均使用低阻抗电源层至关重要。为开关电流提供最低电感的回流路径可确保在目标应用中获得最佳性能。

下面提到的接地层假定 VEE 电源平面在 LVPECL 工作时接地。请注意，对于 ECL 操作，VCC 电源平面将成为接地平面。

对输入和输出电源进行适当旁路也很重要。在每个 VCC 电源引脚到接地层的几英寸范围内放置一个  $1 \mu\text{F}$  的电解旁路电容器。此外，在每个 VCC 电源引脚附近放置多个高质量  $0.001 \mu\text{F}$  旁路电容时应尽可能靠近引脚，并用冗余通孔将电容器连接到接地层。尽量选择寄生电感和 ESR 最小的高频旁路电容器。为提高高频旁路的有效性，应尽量减少寄生布局电感。此外，还要避免输入和输出传输线上的不连续性，以免影响抖动性能。

在  $50 \Omega$  环境中，输入和输出匹配对性能有重大影响。**b uffer** 为 CLK<sub>x</sub> 和 CLK<sub>x</sub> 输入提供内部  $50 \Omega$  终端电阻。通常情况下，返回端连接到所提供的参考引脚。使用陶瓷电容器小心旁路终端电位，以防止终端返回路径中的寄生电感导致输入信号出现不好的畸变。如果输入端与源直流耦合，则应注意确保引脚在额定输入差模和共模范围内。

如果反馈是浮动的，器件会出现 100 的串联，但源极必须控制共模电压并提供输入偏置电流。输入引脚之间装有 ESD/钳位二极管，以防止应用中输入晶体管产生过大偏移。静电放电二极管未针对最佳交流性能进行优化。需要钳位时，建议使用适当的外部二极管。

图 10. 用于连接外露引脚的 PCB 焊盘

## 9.4、应用

### 输入端接选项

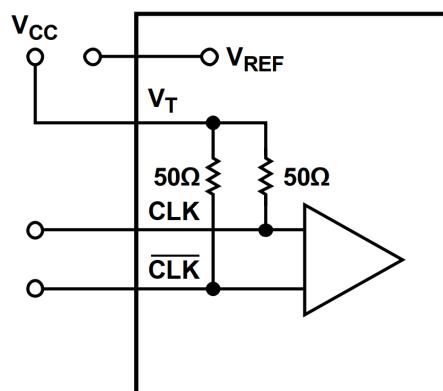

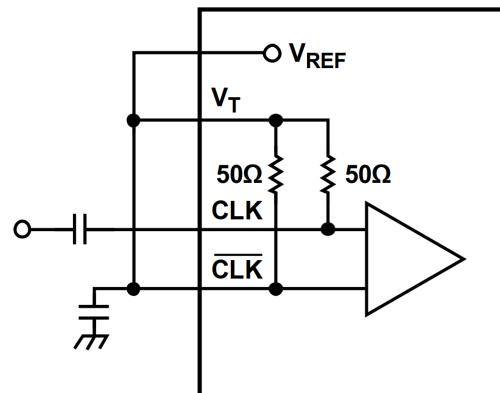

图 11. 链接  $V_T$  到  $V_{CC}$  (与 CML 输入接口)

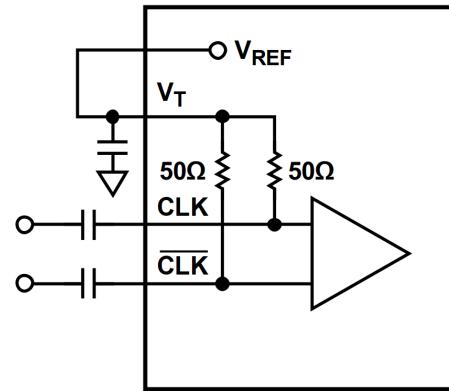

图 12. 链接  $V_T$  到  $V_{REF}$  (交流耦合差分信号输入，如 LVDS)

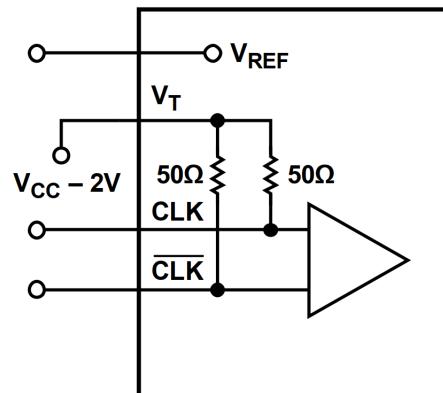

图 13. 链接  $V_T$  到  $V_{CC}-2V$  (与 PECL 输入接口连接)

图 14. 与交流耦合单端输入接口（连接  $V_T$ 、 $V_{REF}$  和  $clk$ 。在  $vt$  和地之间放置一个旁路电容器。或者，也可以将  $vt$ 、 $vref$  和  $clk$  连接起来，这样布局更简洁，相位也会发生  $180^\circ$  的偏移。）

## 10、封装

QFN-24 封装

## 11. 订购信息

| 产品型号     | 工作电压 | 工作频率 (Hz) | 工作温度       | 封装    | 等级  |

|----------|------|-----------|------------|-------|-----|

| XHT-946A | 3.3V | 4.8G      | -55~+125°C | QFN24 | 宽温级 |

| XHT-946B | 3.3V | 4.8G      | -55~+125°C | QFN24 | N1级 |